在我们的日常生活中,数据业务的需求越来越大,随之而来对于通信设施等的带宽要求越来越高。这就需要在一些设备中用到高速的数据采集和数据处理。JESD204正是这样一种用于高速数据采集的接口,目前主要用在ADC和FPGA之间的连接。

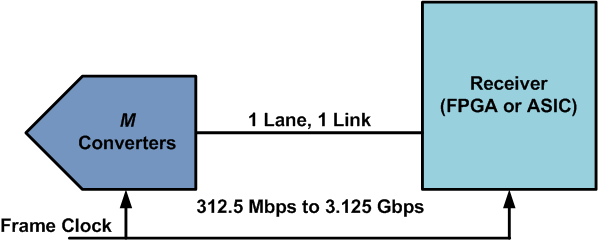

JESD204最初的版本在2006年4月发布,作为转换器和接收器间的串行数据链路。如图1所示,JESD204的结构非常简单,转换器和FPGA之间只有一线连接,其速率最高能够达到3.125Gbps。

图1 JESD204连接示意图

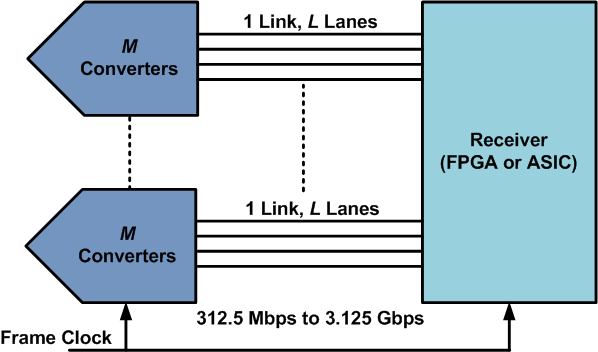

JESD204 的第二个版本于2008年4月发布,命名为JESD204A。该版本对原有标准进行了扩充(如图2所示),可以实现转换器和接收器间多条数据线传输。

图2 JESD204A连接示意图

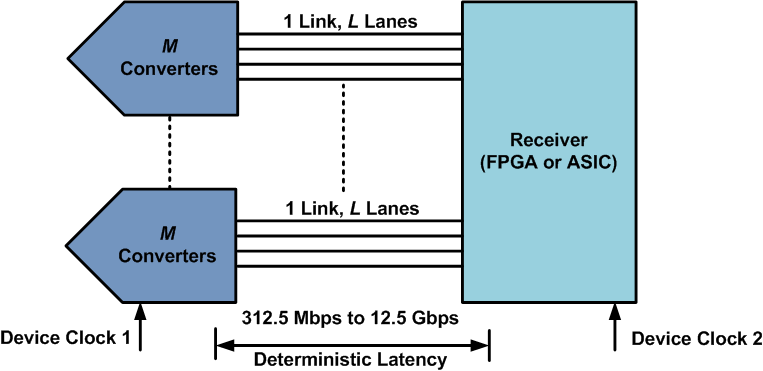

2011年8月,JESD204的第三个版本发布,命名为JESD204B。这一版本在JESD204A的基础上进行了进一步的优化(如图3所示)。JESD204B的时钟不再采用Frame时钟,而是采用设备时钟,使得数据率最高能达到12.5Gbps。

图3 JESD204B连接示意图

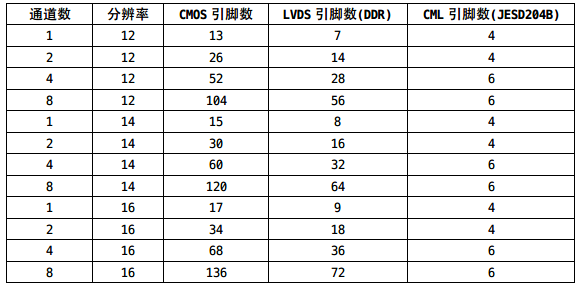

相比以往传统的接口(如CMOS、LVDS等),JESD204B所带来的好处主要有四点:第一,简化系统设计。使用传统的接口时,如果ADC的通道数很多,ADC与FPGA之间的布线将是非常密集的,且需要各通道的布线长度相同——这一点实现相对麻烦——否则将可能使数据质量变差。用JESD204B则可以大大简化ADC与FPGA之间的布线。第二,减少管脚数目。和传统的接口相比,JESD204B能大幅减少管脚数目,从而降低布板的成本,具体管脚数对比可参见下表。

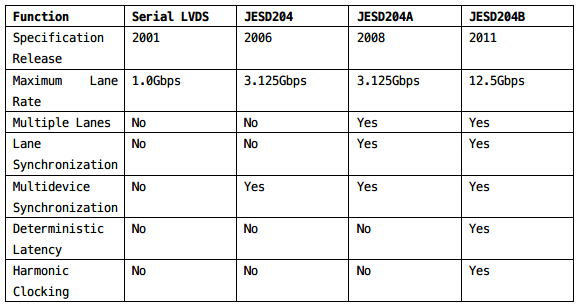

第三,由于布线更简单、管脚数更小,因此,使用JESD204B将会使得封装更小、更简单。第四,JESD204B的数据率优势将带来大带宽。如下所示的表格是LVDS和JESD204各版本在数据率等方面的对比。

目前,JESD204B主要用于转换器和FPGA之间的连接。此前转换器与FPGA之间常见的是LVDS等传统的接口,对于未来JESD204B是否会快速取代LVDS等传统的接口,ADI公司华中区销售经理张靖表示,JESD204B短时间内LVDS和JESD204B还将共存。时下,JESD204B已经出现的主要应用场合包括:3G/4G无线基站等有着高带宽要求的应用;雷达、无线电通信;医疗影像等。针对这些应用,ADI公司推出了一系列相关的JESD20B接口标准的产品。

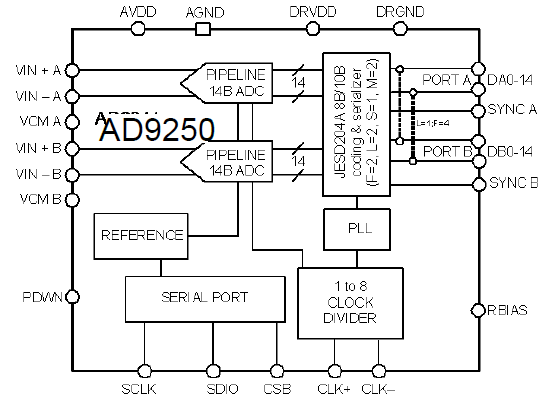

AD9250是ADI公司推出的一款提供JESD204B输出的14位、250 Msps、1.8V、双通道ADC产品。该产品具有良好的宽带性能,低功耗,可以轻松与FPGA连接。

图4 AD9250结构框图

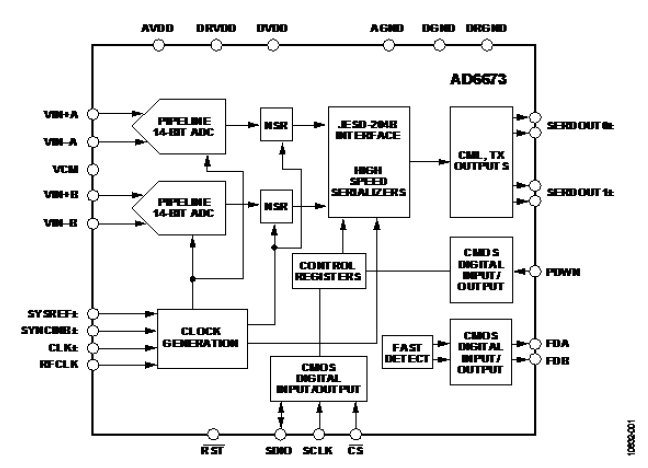

ADI公司还推出了AD6673器件,该产品是一款80 MHz带宽双通道IF接收器,无需出口授权许可,可在中国市场出售。AD6673的主要优势在于其较小的尺寸,同时减少输出引脚数,所需FPGA I/O也更少。

图5 AD6673结构框图

在EEPW网站上有关于JESD204B接口的在线研讨会,链接如下。

http://seminar.eepw.com.cn/seminar/show/id/100

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。